# Mehrkanaliges Aufnahmesystem

Im Rahmen dieses Projekts wurde ein effizientes, multimodales und mehrkanaliges Aufnahmesystem für die Sonova AG konzipiert und einige Aspekte in Form eines Proof of Concept umgesetzt. Im Fokus stand das synchrone Sampeln der Audiodaten der HI-Satelliten.

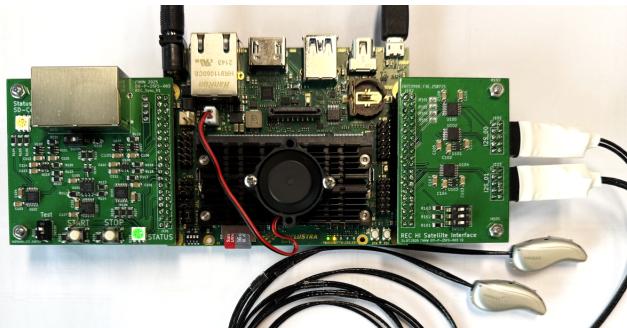

Das In-Design-Development-Board MARS ST3 von Enclustra mit den zwei zusätzlich entwickelten PCBs: dem REC HI Satellite zum Anschliessen der HI-Hörgeräte sowie dem REC Sync für die User-Interaktion und die Schnittstelle zur Synchronisierung mehrerer Systeme.

## Zielsetzung

Ziel war die Entwicklung einer mobilen, digitalen Lösung zur realitätsnahen Erfassung von Audio- und Sensordaten, um Algorithmen in Hörgeräten zu verbessern.

## Konzept

Das System sollte bis zu 22 digitale Audiokanäle sowie verschiedene Sensordaten synchron und präzise aufzeichnen. Neben dem synchronen Aufzeichnen innerhalb eines Geräts sollten auch mehrere Geräte miteinander synchronisiert werden. Eine besondere Herausforderung bestand in der Synchronisierung asynchroner I<sup>2</sup>S-Audiokanäle (RAPS HI Satellites) mit der Primary Clock des Aufzeichnungssystems. Hierzu wurde auf Basis eines Referenzdesigns eines Asynchronous Sample Rate Converters (ASRC) von AMD Xilinx eine Implementierung im FPGA realisiert, die die Eingangssignale von 22,05 kHz auf 48 kHz konvertiert und synchronisiert. Neben der Audioaufzeichnung wurden Konzepte für die Integration mehrerer Sensorkanäle erarbeitet, darunter MEMS-Beschleunigungssensoren, IMUs, PPG-Sensoren, GPS und Videosysteme. Für die Systemsynchronisation wurden verschiedene Ansätze (PTP, PPS, GPS, UWB) analysiert und eine kabelgebundene Referenzclock-Lösung als Favorit für das Proof of Concept gewählt. Das Bedienkonzept umfasst eine Embedded-UI zur Anzeige von Status, Akku, Speicher und Synchronisation sowie zur Durchführung von Konfiguration, Kalibrierung und Selbsttests. Die Hardware basiert auf einem Enclustra-SoM mit AMD Xilinx Ultrascale FPGA.

linx eine Implementierung im FPGA realisiert, die die Eingangssignale von 22,05 kHz auf 48 kHz konvertiert und synchronisiert. Neben der Audioaufzeichnung wurden Konzepte für die Integration mehrerer Sensorkanäle erarbeitet, darunter MEMS-Beschleunigungssensoren, IMUs, PPG-Sensoren, GPS und Videosysteme. Für die Systemsynchronisation wurden verschiedene Ansätze (PTP, PPS, GPS, UWB) analysiert und eine kabelgebundene Referenzclock-Lösung als Favorit für das Proof of Concept gewählt. Das Bedienkonzept umfasst eine Embedded-UI zur Anzeige von Status, Akku, Speicher und Synchronisation sowie zur Durchführung von Konfiguration, Kalibrierung und Selbsttests. Die Hardware basiert auf einem Enclustra-SoM mit AMD Xilinx Ultrascale FPGA.

## Proof of Concept

Im Rahmen des Proof of Concept wurden für die Anbindung externer Geräte zwei eigene Leiterplatten entwickelt: das PCB REC Interface für zwei I<sup>2</sup>S-Audioeingänge und das PCB REC Sync für Synchronisationssignale zweier System und Benutzerinteraktion.

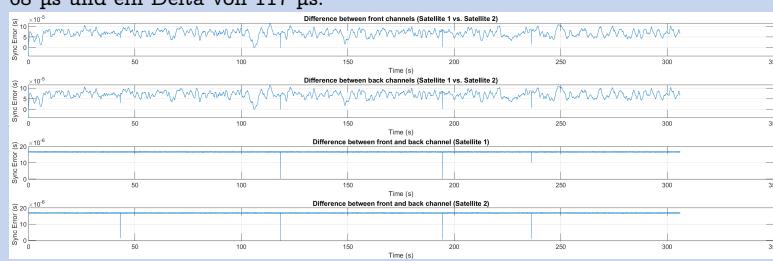

Die Implementierung erfolgte in VHDL (PL-Teil) und C (PS-Teil) unter Verwendung von Vivado und Vitis. Die Verifikation in der Simulation zeigte die erwartete Synchronität innerhalb eines Systems mit zwei I<sup>2</sup>S-HI-Satelliten. Die Messungen, bei denen ein 1-kHz-Sinus aufgezeichnet und mit Hilfe der Nulldurchgänge die Synchronität ermittelt wurde, zeigten, dass der Clock-Drift der zwei I<sup>2</sup>S-Systeme kompensiert wurde, jedoch ein Offset zwischen den Kanälen besteht.

## Infobox

Auswertung eines Systems, das mit zwei Satelliten, somit zwei asynchronen I<sup>2</sup>S-Audiokanälen mit je zwei Mikrofonen, ein 1 kHz Sinussignal aufgezeichnet hat. Die Grafik vergleicht die Nulldurchgänge miteinander. Innerhalb eines Satelliten besteht ein konstanter Offset von ca. 17  $\mu$ s. Vergleicht man zwei Satelliten, sind Offset und Varianz grösser und betragen einen durchschnittlichen Offset von 68  $\mu$ s und ein Delta von 117  $\mu$ s.

## Arbeitsgruppe:

Lukas Kappeler

## Auftraggeber:

Sonova AG, Stäfa

## Betreuer:

Prof. Michael Pichler